-

English

English -

Français

Français

-

Deutsch

Deutsch

-

اللغة العربية

اللغة العربية

16Bits ADC 8CH Sinchronizavimo AD7606 DUOMENŲ kaupimo Modulis 200Ksps

€13.85

-10%

€15.39

Nauja prekė

1 Prekės

Žymos: adc, 16 bitų adc, adc 16 bitų delta, adc garso, įsigijimo duomenys, 24 bitų adc, 12 bitų adc, adc spi, ads1115, ad7606.

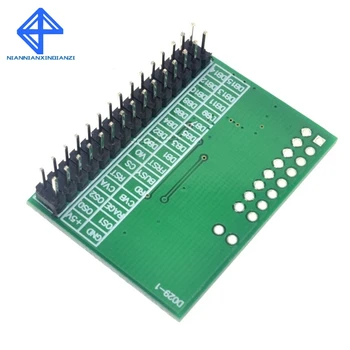

Patarimas : Norėdami palengvinti jūsų pasirinkimą , PCB lenta analoginis įėjimas priekyje -eilė pin (2x8/2.54 mm žingsnio ) numatytasis ne suvirinimo .Mes išdalinsime 2x8 's dviguba adata ir aštuonių džemperiai, kad klientas savo nuožiūra yra iki virinimo, litavimo ar žemyn .

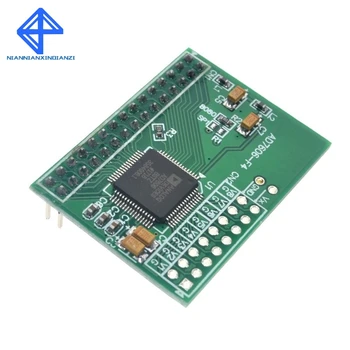

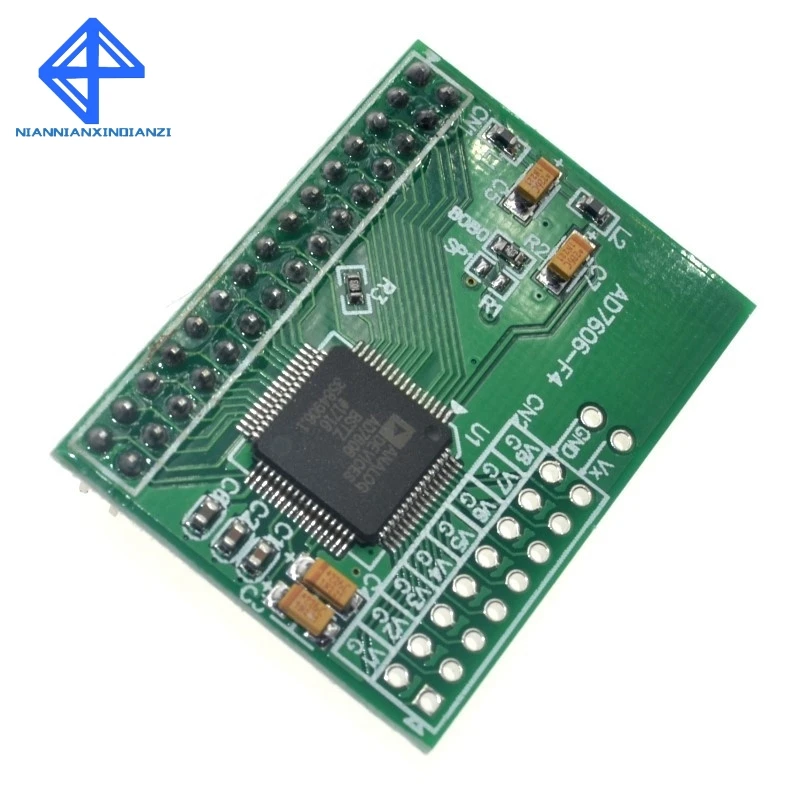

1, naudojant didelio tikslumo 16-bitų ADC chip AD7606

2,8 analoginius įėjimus. 1M omų varža.[Nėra neigiamas pasiūlos, nėra front-end analoginis stiprintuvas gali būti prijungtas tiesiogiai prie jutiklio išvestis]

3, įvesties diapazonas plius arba minus 5V, plius arba minus 10V.By IO kontrolės.

4, Rezoliucija 16.

5, maksimalus mėginių ėmimo dažnumas ėminių ėmimo dažnis 200ksps.Palaiko aštuonių mėginių ėmimo parametrų failą (kuris gali efektyviai sumažinti jitter)

6, built-in etalonas

7, vieną 5V maitinimo šaltinis

8, SPI Sąsaja, arba 16 bitų magistralės sąsaja.Sąsaja IO lygis gali būti 5V, arba 3,3 V. Mes AD7606 modulis gamykliniai 8080 lygiagrečios sąsajos.

Jei SPI sąsajos režimą, reikia pakeisti R1 R2 rezistorius konfigūracijos.

Lygiagrečiai Režimas Megztinis: R1 kintama (ne lipdukas), R2 10K rezistorius pasta

SPI sąsaja režimas megztinis: R1 lipdukai 10K rezistorius R2 kintama (ne lipdukai)

AD7606 konfigūracija yra labai paprasta, jis neturi vidaus registrus.Asortimentas ir daugiau-imčių parametrų yra kontroliuojama per išorinį IO.

Impulsų dažnis, mėginių ėmimo normos, jeigu mikrokontrolerio ar DSP valdymo.

AD7606 turi naudoti vieną 5V maitinimo.

Lygis ryšio sąsajos tarp AD7606 ir AUKŠTESNIOSIOS kontroliuoja VIO pin.Kad VIO maitinimas turi būti prijungtas prie mikrovaldiklis gali būti 3.3 V, taip pat gali būti 5V.

[Modulio Pin Aprašymas]

OS2 OS1 OS2: derinys valstybės atrankos perdiskretizavimą režimu.

000-tai ne perdiskretizavimą, didžiausia ėminių ėmimo dažnis 200ksps.

001 atstovauja du kartus perdiskretizavimą, kuris yra aparatūros viduje surinkti du mėginiai vidutiniškai

010 yra keturis kartus perdiskretizavimą, kuris yra aparatūros viduje rinkti keturi mėginiai vidurkis

011 yra aštuonis kartus perdiskretizavimą, kuris yra aparatūros viduje surinkti aštuoni mėginiai vidurkis

100 yra 16 kartų perdiskretizavimą, kuris yra aparatūros viduje surinkti 16 mėginių vidurkis

101 yra 32 kartus perdiskretizavimą, kuris yra vidinis aparatūros vidutiniškai surinktų mėginių 32

110 sudaro 64 kartus perdiskretizavimą, kuris yra aparatūros viduje surinkti 64 mėginių vidurkis

Perdiskretizavimą santykis yra didesnis, tuo ilgiau ADC konversijos metu, tuo mažesnis maksimalus mėginių ėmimo dažnumą galima gauti.

CVA, CVB: SKELBIMŲ konversijos paleidimo valdymo signalo kanalą 1-4 sprendimas CVA, CVB nusprendė 5-8 kanalai.

Du signalus galima išskirstyti per trumpą laiką, apskritai, gali būti CVA, CVB lygiagrečiai kartu.

PYKTIS: Pasirinkite nuo 0 reiškia, pridėjus arba atėmus 5V, 1 rodo neigiamą 10V.

RD: Skaityti signalas

RST: Reset signalas

Užimta: Užimtas Signalas

CS: chip-pasirinkite signalo

FRST: pirmasis kanalas mėginius, nurodant signalas

VIO: ryšių sąsaja lygis

DB0 - DB15: Duomenų Magistralės

[16 lygiagrečiai režimu elektros instaliacijos schema --- AD7606 taip pat palaiko 8-bitų magistralės režimu, žr AD7606 duomenų lapas

MCU pusėje AD7606 modulis

GND GPIO įvesties AD606 yra konvertuojami instrukcijos. [Rekomenduojama ryšį su išorės pin nutraukti pajėgumų]

CS 8080 duomenų magistralės (16)

FRST gali imtis

[SPI sąsajos režimą, elektros instaliacijos schema

MCU pusėje AD7606 modulis

GND GPIO įėjimas, AD606 yra konvertuojami instrukcijos. [Rekomenduojama ryšį su išorės pin nutraukti pajėgumų]

CS SPI autobusų duomenų linijų sojų pasta

DB14 - DB15 gali pasiimti

FRST gali imtis

Programinės įrangos diegimas [1] --- laikas įsigyti SPI pavyzdžiui, mes siūlome dokumentas, naudojant šią programą, žr. bsp_spi_ad7606.c

Į laikmatis nutraukti paslaugų įprastas įgyvendinimo:

Laikmatis nutraukti ISR:

{

Nutraukti įrašo;

8 skaito mėginių rezultatai yra saugomi RAM kanalo; ----> skaityti yra paskutinis įrašų kolekcija nuolat įsigijimo, jis nėra susijęs su

Pradėti kitą ADC įsigijimo; (flip CVA ir CVB)

Nutraukti grįžti;

}

Laikmatis dažnis yra ADC mėginių ėmimo dažnis.Šis režimas negali prisijungti užimtas uosto kabelis.

Programinės įrangos diegimas [2] --- laikina 8080 įsigijimo sąsaja pateikiame pavyzdį, naudojant šią programą, žr. bsp_ad7606.c failų

Konfigūruoti CVA CVB pin PWM išėjimo režimas, mėginių ėmimo laikotarpis yra nustatyti norimą dažnį; ---> Po MCU gamins labai stabilus SKELBIMŲ konversijos ciklą signalas

Užimtas uosto linija nustatyta, kad nutraukia kritimo krašto sukelti režimas;

Išorės nutraukti ISR

{

Nutraukti įrašo;

8 skaito atrankos rezultatus kanalo saugomi RAM;

Nutraukti grįžti;

}

[1 ir 2, skirtumai įdiegti programinę įrangą-laikas įsigyti]

(1) 1 Variantas gali būti mažiau užimtas linijos, bet ir kitų pagrindinių nutraukti paslaugų rutinos ar laikini pasaulio nutraukti, kai ADC konversijos ciklą, gali sukelti šiek tiek drebėjimas.

(2) 2 Variantas gali užtikrinti stabilumą įsigijimo laikrodžio, nes jis yra sukurtas MCU aparatūros, bet reikia daugiau tada UŽIMTAS burnos linijos.

Pakuotė: 1 VNT x 16Bits ADC 8CH Sinchronizavimo AD7606 DUOMENŲ kaupimo Modulis 200Ksps

| Darbinė Temperatūra | ad7606 |

| Pakuotė | CINKAVIMAS |

| Modelio Numeris | ad7606 |

| sąlyga | Naujas |

| Prekės Pavadinimas | EQV |

| Tipas | ad7606 |

| Išsklaidymo Galia | ad7606 |

| Maitinimo Įtampa | ad7606 |

| Prašymas | ad7606 |